**Advanced System Technologies**

# Hardware Accelerated Human Pose Estimation

Human Pose Estimation (HPE) erkennt ein kinematisches Modell des menschlichen Körpers aus Bilddaten.

Das Interdisziplinäre Zentrum für Künstliche Intelligenz (ICAI) an der OST hat das bekannte HPE Netzwerk OpenPose weiterentwickelt und rechnerisch effizienter gemacht. Mitarbeitende des IMES Institut für Mikroelektronik, Embedded Systems und Sensorik haben das ICAIPose auf einer FPGA-Hardware beschleunigt.

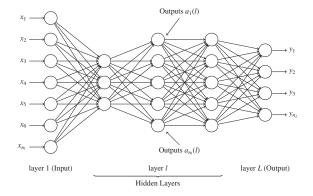

FullyConnected Layers

Convolutional and Pooling Layers

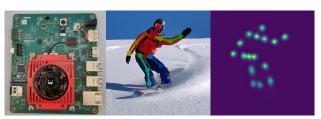

ICAIPose on the Kira KV260 Board

#### Ziel

Mitarbeitende des IMES haben das ICAIPose-Projekt erfolgreich auf dem Edge FPGA Kria KV 260 von AMD-Xilinx implementiert. Durch die Übertragung des ICAIPose von herkömmlichen Grafikkarten auf ein FPGA konnte der Aufwand für den Betrieb des Netzwerks minimiert werden, ohne die Performance zu beeinträchtigen. Das IMES hat nicht nur die technische Realisierbarkeit dieses Vorhabens demonstriert, sondern auch die potenziellen finanziellen und praktischen Vorteile einer FPGA-basierten Lösung im Vergleich zu herkömmlichen GPU-basierten Ansätzen ermittelt.

### Vorgehen

Für das Projekt wurde eine Kamera-Schnittstelle mit einer Deep-Learning-Verarbeitungseinheit erfolgreich integriert. Hierbei wurde Vitis Al von AMD-Xilinx verwendet, um das Netzwerk für die Deep Learning Prozessoreinheit (DPU) auf dem FPGA zu kompilieren. Die Python-API, die Teil des Pakets ist, ermöglichte eine reibungslose Kommunikation mit der DPU über ein eingebettetes Linux auf dem Mikroprozessor des FPGAs. Es wurden umfangreiche Tests und Optimierungen durchgeführt, um eine bestmögliche Leistung und Effizienz zu erzielen.

### Fazit

ICAIPose ist ein äusserst komplexes neuronales Netzwerk, das für die Verarbeitung eines einzelnen Bildes mehr als 100 Milliarden Operationen benötigt. Trotz dieser enormen Anforderungen erreicht das Kria KV260 eine beeindruckende Bildrate von 8 Bildern pro Sekunde. Diese Tatsache unterstreicht die FPGA-Lösung sowie die Leistungsfähigkeit des Kria KV260. Im Vergleich dazu erreicht das GPU-basierte NVIDIA Jetson Xavier NX, das mehr als doppelt so viel kostet wie das Kria-Board, eine ähnliche Bildrate. Die erfolgreiche Implementierung des ICAIPose auf dem Kria KV260 demonstriert das enorme Potenzial der FPGA-Technologie für komplexe Deep-Learning-Anwendungen und eröffnet somit neue Möglichkeiten für zukünftige Entwicklungen in diesem Bereich.

ost.ch/imes

## Kontakt

Prof. Dr. Paul Zbinden

OST – Ostschweizer Fachhochschule,

IMES Institut für Mikroelektronik, Embedded Systems und Sensorik

Oberseestrasse 10, 8640 Rapperswil

+41 58 257 45 84, paul.zbinden@ost.ch